# Conductive through silicon via holes for RF applications

D. Vasilache, S. Colpo, M. Chistè, F. Giacomozzi, B. Margesin

FBK-irst Trento, Via Sommarive 18, 38123 Povo Trento, Italy

#### Introduction

Manufacturing method

**Process optimization**

Gold electroplating

#### **Introduction**

- Emphasis of the systems on chip (SOC) and in package (SIP) required the development of 3D encapsulation methods; a great efforts been made microelectronic devices miniaturization, higher and higher packaging densities being required

- Through-silicon interconnection technology is considered to be a critical and enabling technology for 3-D stacking of electronic and electro-mechanical systems

Manufacturing involve two problems: through wafer via holes manufacturing and holes filling with a conductive layer.

Via holes manufacturing methods: anisotropic wet etching, powder blasting, laser ablation, laser melt cutting or deep reactive ion etching (DRIE); geometries with aspect ratio between 1 and 20.

From all fabrication techniques DRIE shows its superiority in respect of pattern transfer and minimum dimensions – aspect ratio even bigger than 20 it is possible to achieve, while the accuracy will be provided by the photolithography.

#### Conductive layer / via holes filling:

- > copper critical advantage of being able to fill high-aspect ratio holes by electroplating

- > polysilicon heavily doped, conformal deposition by low-pressure chemical vapor deposition (LPCVD)

- ➤ the alternative is to use gold as conductive layer poor adhesion to dielectrics and the need for barrier and/or adhesion layers

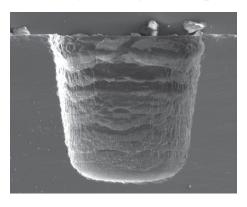

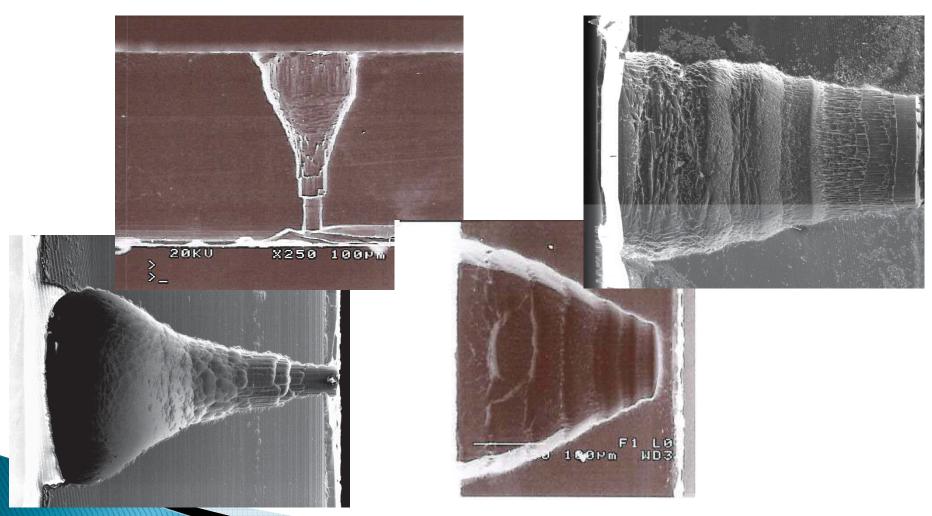

Our aim was to use gold as conductive layer; tapered walls - allow to deposit barrier and seed layer (CrAu) by PVD techniques

Introduction

Manufacturing method

Process optimization

Gold electroplating

#### Manufacturing method

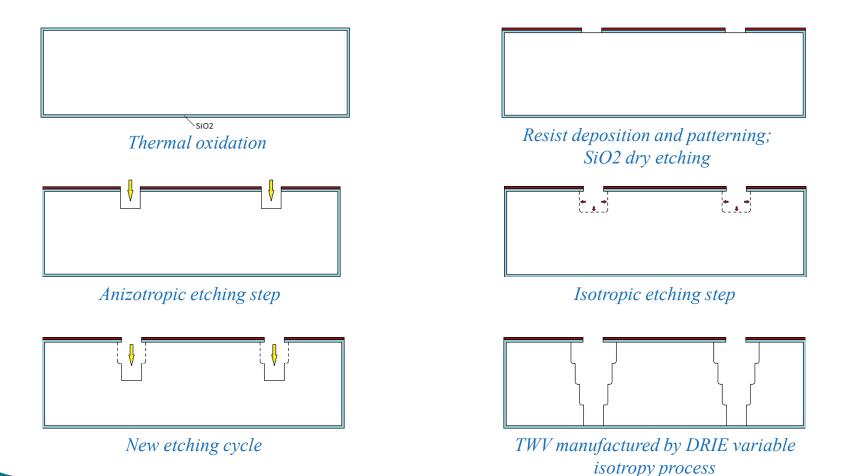

• based on the possibility to change the process isotropy

Transition from one process type to another can be achieved by changing the plasma composition and can be performed during the same processing step.

By mixing the basic processes (anisotropic and isotropic) it is possible to obtain new shapes, unique, that cannot be obtained by other techniques.

#### DRIE processing main steps:

- anisotropic etching (Bosch process type) to achieve the via depth

- isotropic etching to enlarge via

- plasma oxygen (before isotropic etching) to remove the passivation from the walls

Etching cycles are repeated until the opposite wafer surface is reached.

The via holes shape – strongly influenced by the number of anisotropic/isotropic etching cycles used and length of each etching step.

Size of the holes (diameter) is given by the initial etching window on one side, while on the opposite side will be greater, being influenced by the number and length of isotropic etching steps used.

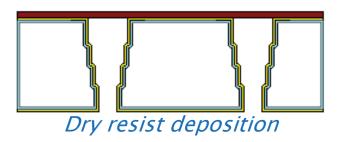

#### Schematic view of the technological flow

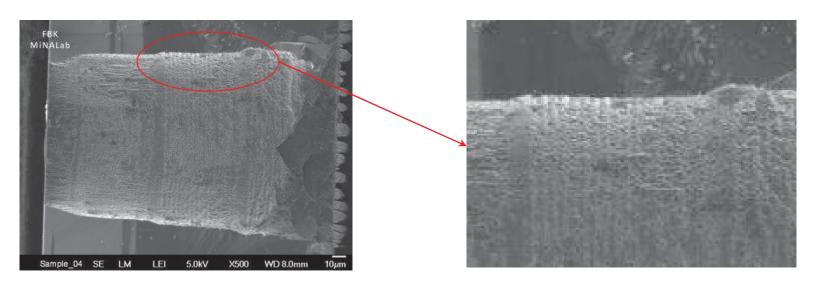

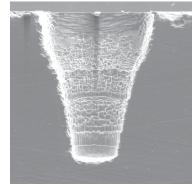

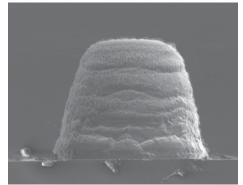

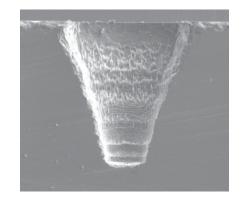

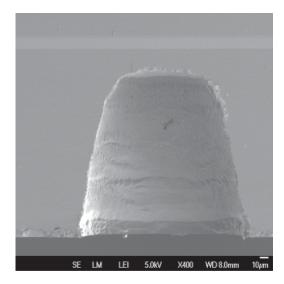

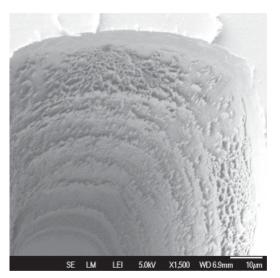

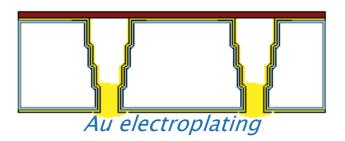

SEM photos of the manufactured TSVs using 200 microns thick wafers.

Introduction

Manufacturing method

Process optimization

Gold electroplating

#### **Process optimization**

- > rating of etching rate of each process type anisotropic & isotropic

- > wall roughness reducing by using various types of anisotropic etching recipes

- > optimization considering depth attenuation

- ✓ARDE effect (Aspect Ratio Dependant Etching) different opening etching sizes provide us extremely different etching rates; 20µm & 100µm diameter

- ✓ three different anisotropic etching recipes were used

- ✓ various types of wafers were used, with thicknesses between 200 and 500 microns

#### First optimization step

- etching windows 100μm

- anisotropic etching → HER (High Etching Rate)

- measured etching rates:

- anizotropic etchings ~17,33μm/min

- isotropic etchings ~2μm/min.

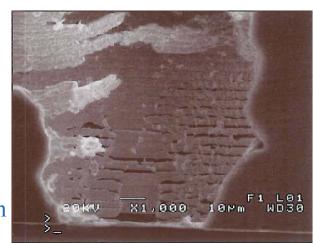

After metalization

#### Second optimization step

- etching windows  $20\mu m \& 100\mu m$

- anisotropic etching recipes SDE\* & LR\*\*

- targeted wall angles  $-21.8^{\circ}$

- depth target  $-200\mu m$  (for  $100\mu m$  diameter etching windows)

- \* SDE Silicon Deep Etching (smaller gas flow/pressure and power; higher substrate bias)

- \*\* LR Low Roughness (gas flow/pressure and power greatly reduced)

20μm and 100μm diameter cavities – SDE recipe

- $depth \rightarrow 160 \mu m \div 200 \mu m$  for  $100 \mu m$  diameter etching windows and  $110 \mu m \div 130 \mu m$  for  $20 \mu m$  diameter, depending of anisotropic etching recipe

- lateral etching  $\rightarrow \sim 48 \mu m$  for  $100 \mu m$  and  $\sim 30 \mu m$  for  $20 \mu m$

- measured angles  $\rightarrow 14^{\circ} \div 18^{\circ}$

- for  $20\mu m$  etching rates smaller by 35% comparing with  $100\mu m$  diameter etching windows

- very low roughness not only the effect of changing the anisotropic etching recipe, but also due to longer isotropic etchings to obtain higher angles; nanometer peaks on the walls

Last optimization step  $-20\mu m$  &  $100\mu m$  diameter etching windows; aspect ratio  $\rightarrow$  up to 15:1; targeted angles  $\rightarrow$  11,3° (60 $\mu m$ ) si 21,8° (120 $\mu m$ )

Conferinta Diaspora in Cercetarea Stiintifica si Invatamantul Superior din Romania Bucuresti, 25-23 Septembrie 2012

Measurements have revealed very good agreement between design and experiment.

|                   | Mask diameter |              |          |          |

|-------------------|---------------|--------------|----------|----------|

| Parameter         | 20μm          |              | 100μm    |          |

| Target angle      | 11.3 °        | 21.8°        | 11.3 °   | 21.8°    |

| (lateral etching) | (60μm)        | $(120\mu m)$ | (60μm)   | (120µm)  |

| Bottom size       | ~25µm         | ~27µm        | ~140µm   | ~100µm   |

| Top size          | ~134µm        | ~190µm       | ~252µm   | ~330µm   |

| Measured angle    | ~10.3 °       | ~15.2°       | ~10.57 ° | ~20.97 ° |

| Error             | ~9.17%        | ~31.7%       | ~6.67%   | ~4.17%   |

DRIE variable isotropy process for TWV manufacturing allow a very good control of the wall angles, it is reiterative, process optimization being easy to achieve, demanding minimal resources and a short time.

Introduction

Manufacturing method

Process optimization

Gold electroplating

# Conductive TWV manufacturing using gold electroplating

Conferenta Diaspora in Cercetarea Stiintifica si Invatamantul Superior din Romania Bucuresti, 25-23 Septembrie 2012

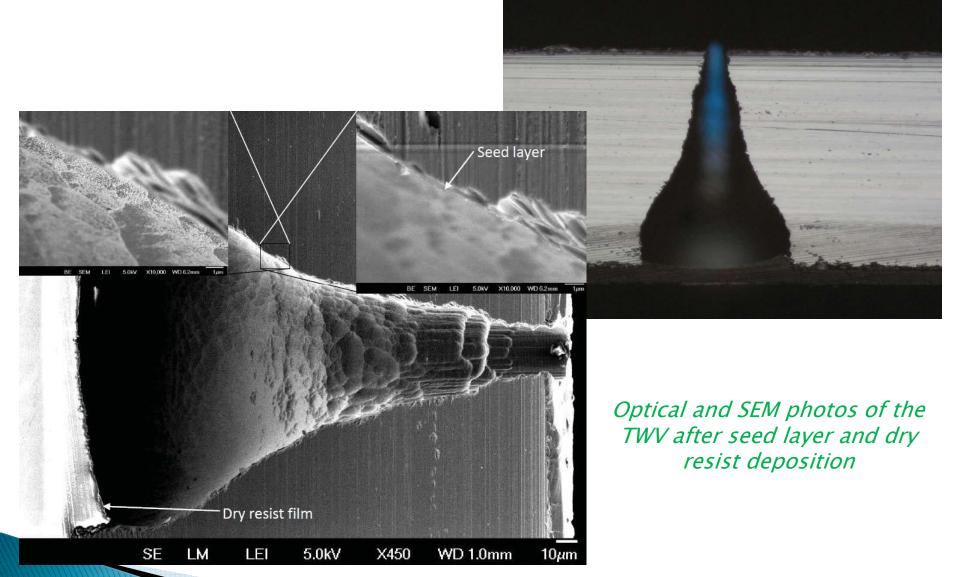

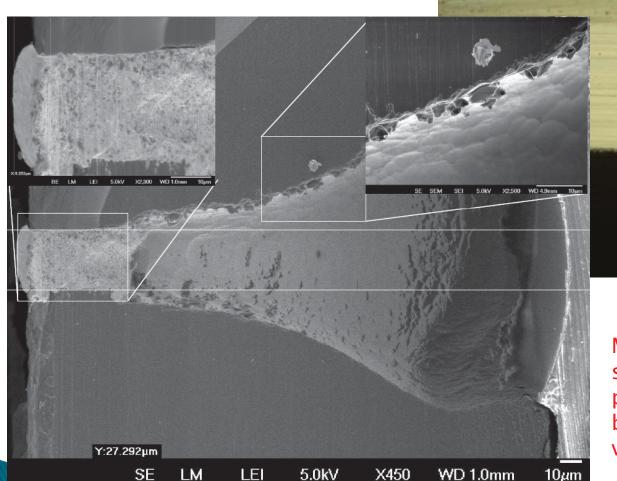

Optical and SEM photos of the TWV after Au electroplating

Measurements performed showed that the whole narrow part was filled on a depth between 50 and 70µm for all via's.

Introduction

Manufacturing method

Process optimization

Gold electroplating

#### **CONCLUSIONS**

- a new method to obtain conductive through wafer via's was presented

- tapered TWV were manufactured by DRIE using a variable isotropy process, allowing a very good control of the wall angles

- a very good coverage of the via walls by seed and barrier layers was demonstrated

- $\bullet$  gold electroplating was used to fill the narrow part of the via's on a depth of at least  $50\mu m$

- obtained structures, even partially filled, allow a subsequent processing of the wafer at least on one side.